# iVAMS: A Paradigm Shift System Simulation Framework for the IoT Era

Saraju P. Mohanty

NanoSystem Design Laboratory (NSDL)

Dept. of Computer Science and Engineering

University of North Texas, Denton, TX 76203, USA.

Email: saraju.mohanty@unt.edu

#### **Smart Cities**

70% of the world population will live in urban areas by 2050.

**Smart Cities**

- ← Cities

- + ICT

- + Smart Components

Refer: http://smartcities.ieee.org

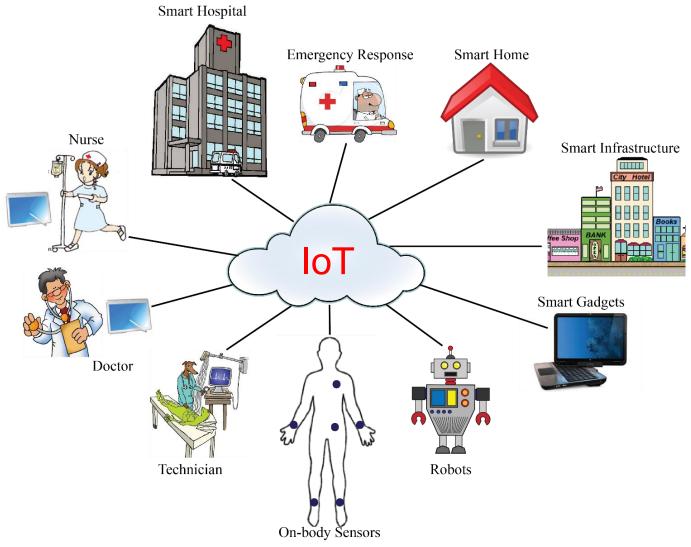

#### **Smart Health Care**

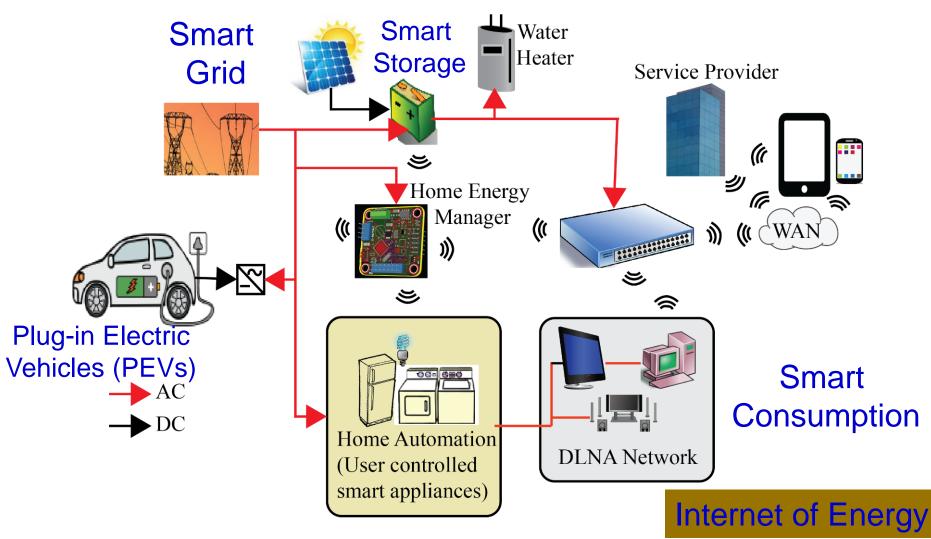

### **Smart Energy**

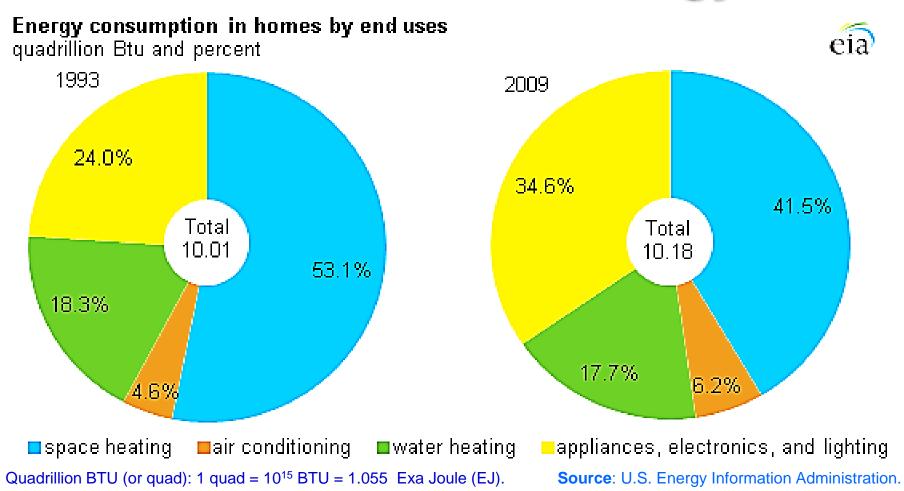

# Consumer Electronics Demand More and More Energy

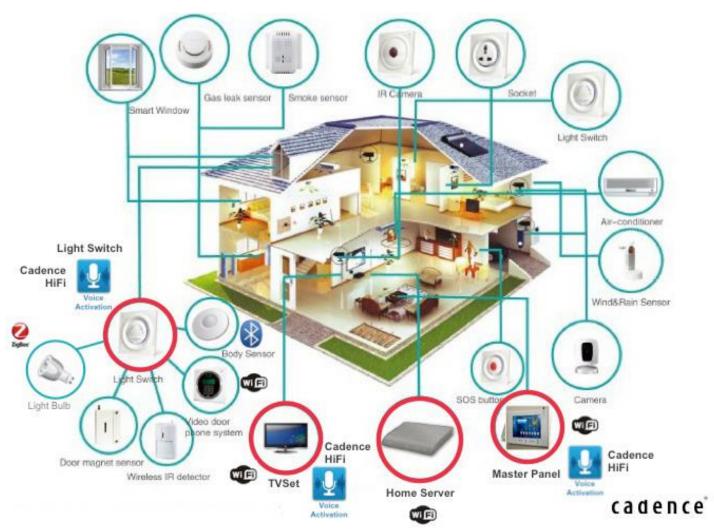

#### **Smart Home**

Source: Cadence

#### What Makes Smart Cities Feasible?

3 key features of Smart Cities come from IoT:

- Intelligence

- Interconnection

- Instrumentation

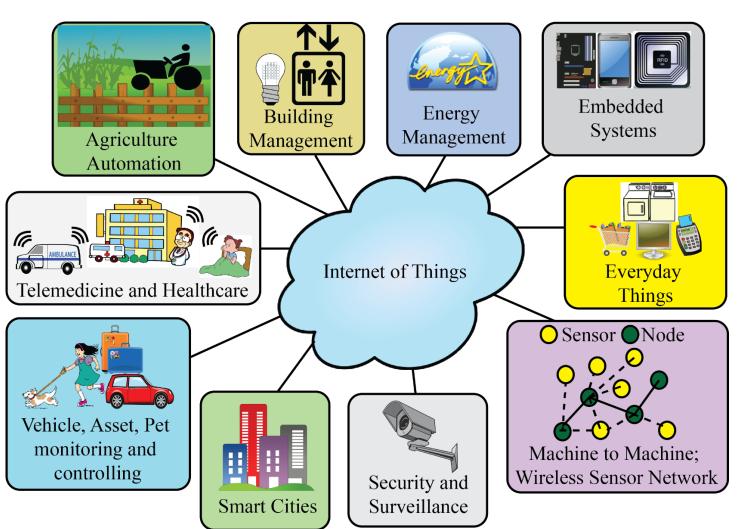

#### Internet of Things: Architecture

of things.

Local Area Network (LAN)

Internet

The Things

The Cloud

- Overall architecture:

- ❖ A configurable dynamic global network of networks

- Systems-of-Systems

UNT

# Internet of Things: Challenges ...

- Massive Scaling

- Architecture and Dependencies

- Creating Knowledge and Big Data

- Robustness

- Security and Privacy

- Energy Consumption

- Design and Operation Cost

- ❖75 billion connecting devices by 2020.

- Eventually trillions of things.

### Internet of Things: Challenges

- Traditional controllers and processors do not meet loT requirements, such as multiple sensor, communication protocol, energy consumption, and security requirements.

- Existing tools are not enough to meet challenges like time-to-market, complexity, design cost of IoT.

- Can a framework be developed for simulation, verification, and optimization:

- of individual (multidiscipline) "Things"

- of IoT Components

- of IoT Architecture

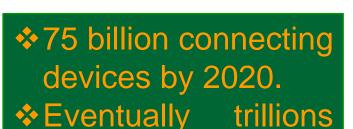

# How to Handle DfX in IoT Design?

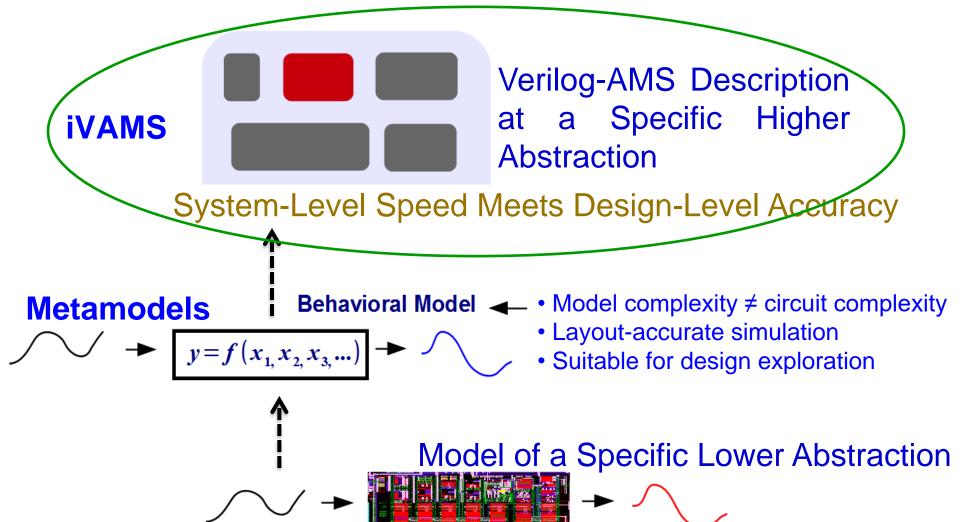

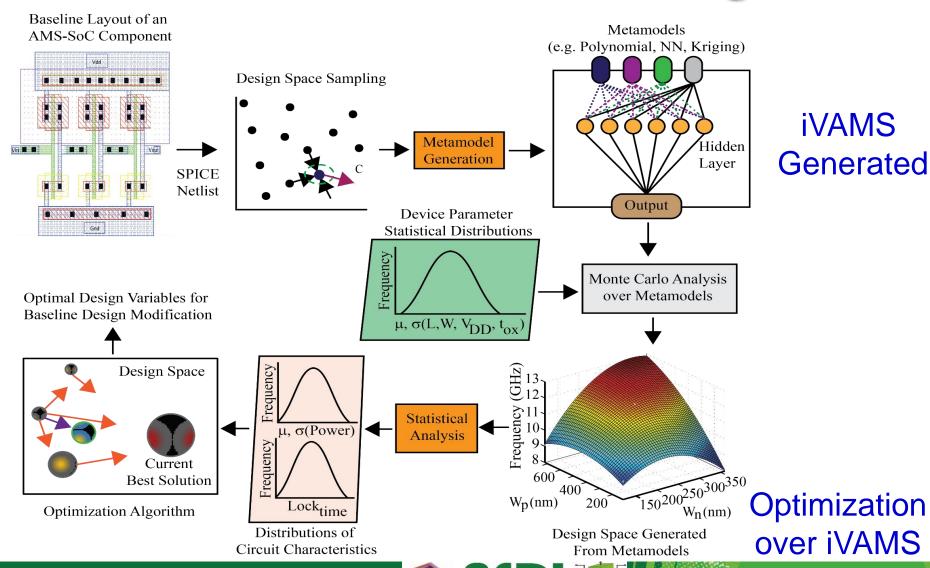

#### A Solution - iVAMS

#### iVAMS code: OP-AMP Example

```

function real NN metamodel; ... ...

integer \alpha_1, \beta_2, b_1, b_2, i, j, readfile, ...; real w, b, v, u;

// Read metamodel weights and bias from text files.

// \alpha_1, \beta_2, b_1, and b_2.

... v = 0.0;

for (j = 0; j < n1; j = j + 1)

begin

u = 0.0;

for (i = 0; i < size x; i = i + 1)

begin

readfile = \$fscanf(w1, "%e", w); u = u + w * x[i];

end

readfile = $fscanf(w2, "%e", w); readfile = $fscanf(b1, "%e", b);

v = v + w * tanh(u + b);

end

readfile = $fscanf(b2, "%e", b);

NN metamodel = v + b; ... ...

end function

```

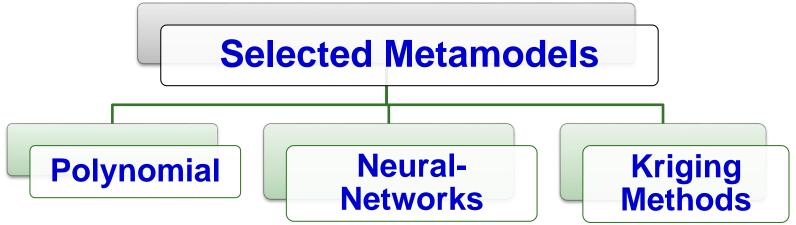

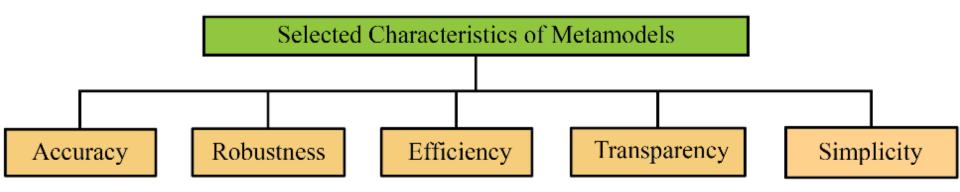

#### What are Metamodels?

"Model of a model" -- Metamodels are mathematical function(s) used to represent the computer simulation models – e.g. polynomial functions, DOE predictive functions, neural networks, and Kriging interpolation:

$$\hat{F}(x_n) = F(x_n) + \varepsilon \approx F(x_n)$$

A green light to greatness.

### **iVAMS**: Key Characteristics

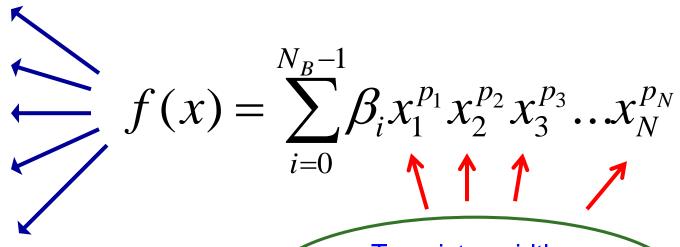

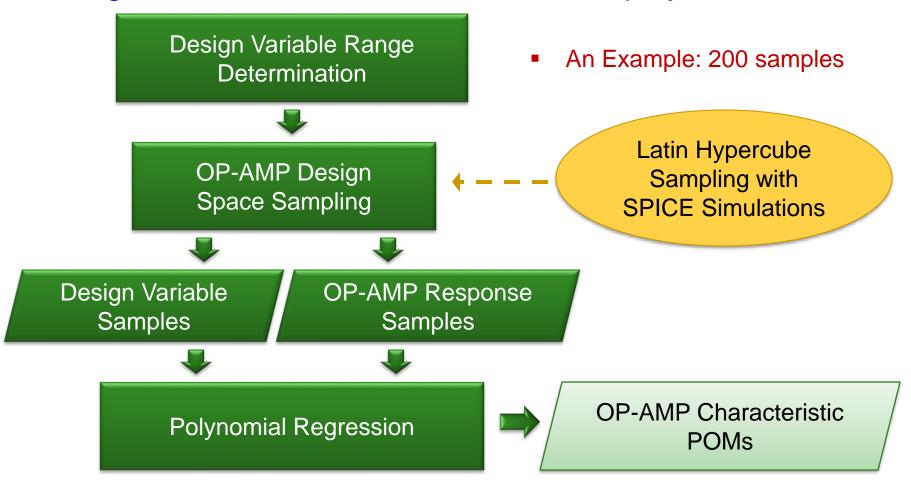

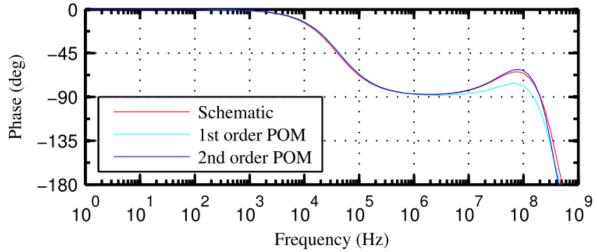

# iVAMS: Polynomial Metamodel (POM)

The OP-AMP characteristics are estimated using POlynomial Metamodel (POM).

Gain

Bandwidth

Phase Margin

**Slew Rate**

Power

- .

- .

- •

Transistor widths, lengths, bias current,

. . .

#### **OP-AMP POM Generation**

The goal is to find the coefficients for the polynomials.

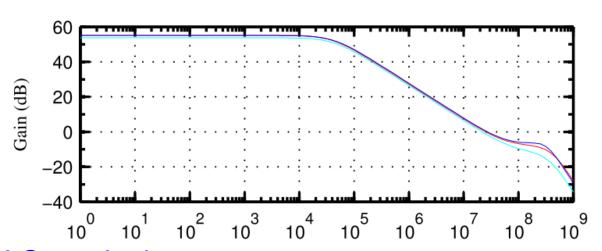

#### **iVAMS: Accuracy Analysis for OP-AMP**

Example: AC analysis

Frequency

### Case Study Electronic Design: PLL

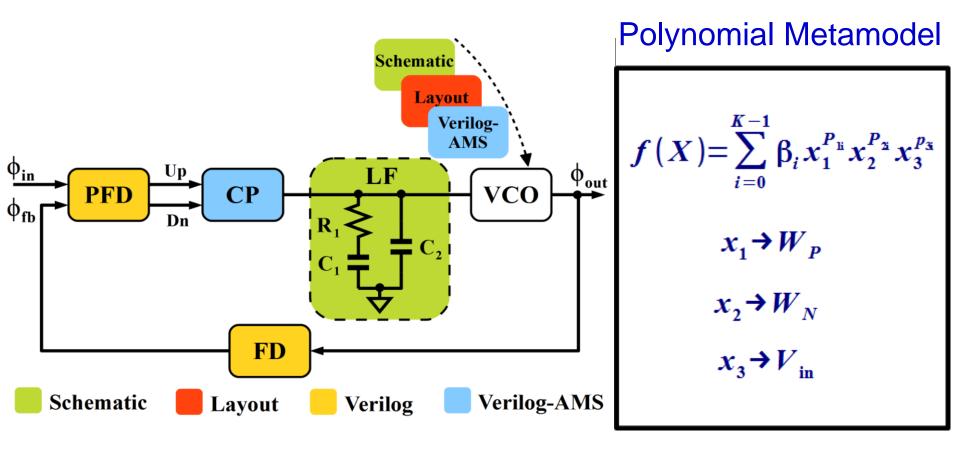

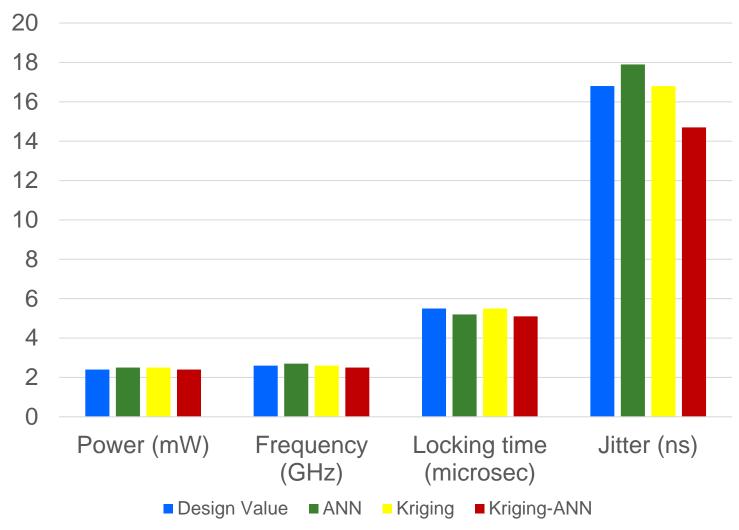

### iVAMS: Accuracy Analysis for PLL

iVAMS is capable of layout-accurate PLL design characteristics such as, center frequency, power dissipation, and jitter.

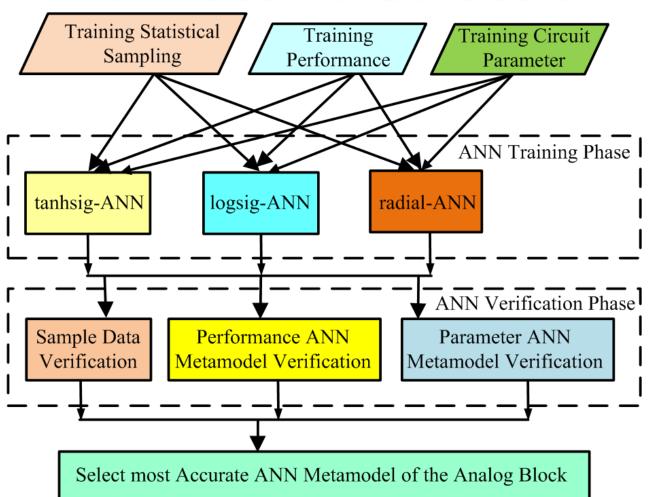

# iVAMS: NN Metamodel Architecture Selection

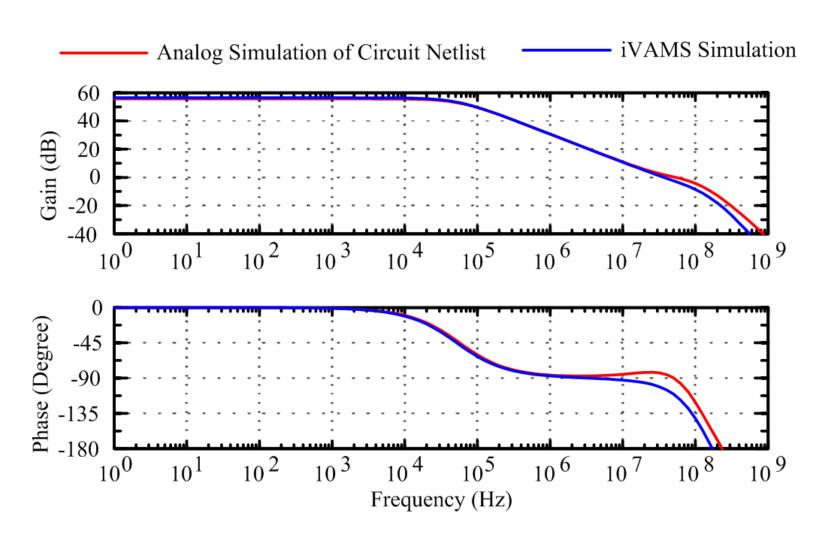

### iVAMS: AC Analysis for Comparison

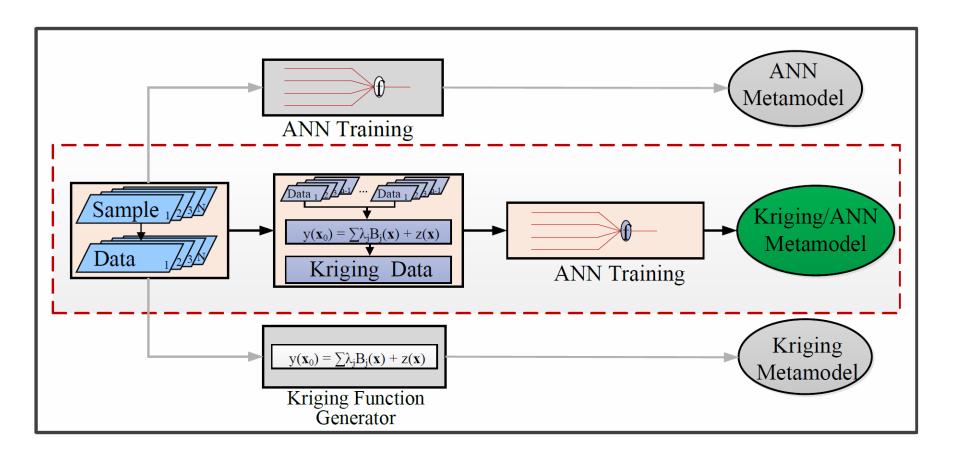

#### Kriging Bootstrapping NN Metamodel

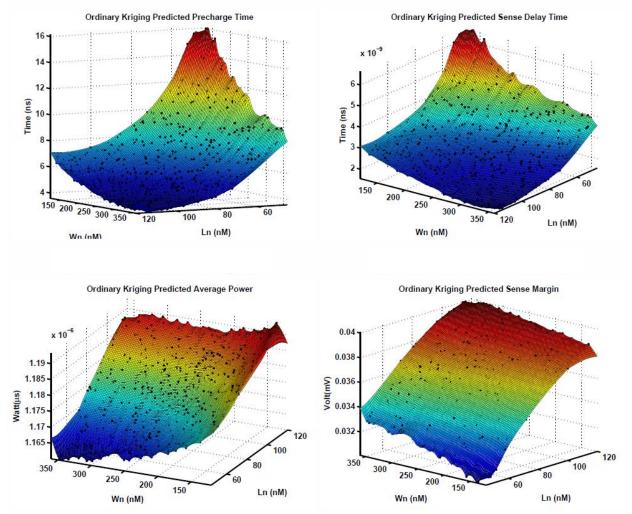

#### **Ordinary Kriging Metamodels**

For a Sense Amplifier Design

# Metamodel Comparison: Polynomial Vs Nonpolynomial

180nm CMOS PLL with Target Specs: f = 2.7GHz, P = 3.9mW,  $8.5\mu s$ .

| Figures-of-<br>Merits (FoM) | Polynomial # of Coefficients RMSE |          | Nonpolynomial (Neural Network) |

|-----------------------------|-----------------------------------|----------|--------------------------------|

| Frequency                   | 48                                | 77.9 MHz | 48 MHz                         |

| Power                       | 50                                | 2.6 mW   | 0.29 mW                        |

| Locking Time                | 56                                | 1.9 μs   | 1.2 μs                         |

- 56% increase in accuracy over polynomial metamodels.

- On average 3.2% error over golden design surface for NN metamodels.

- Nonpolynomial is more suitable for large design.

## Nonpolynomial Metamodel Accuracy

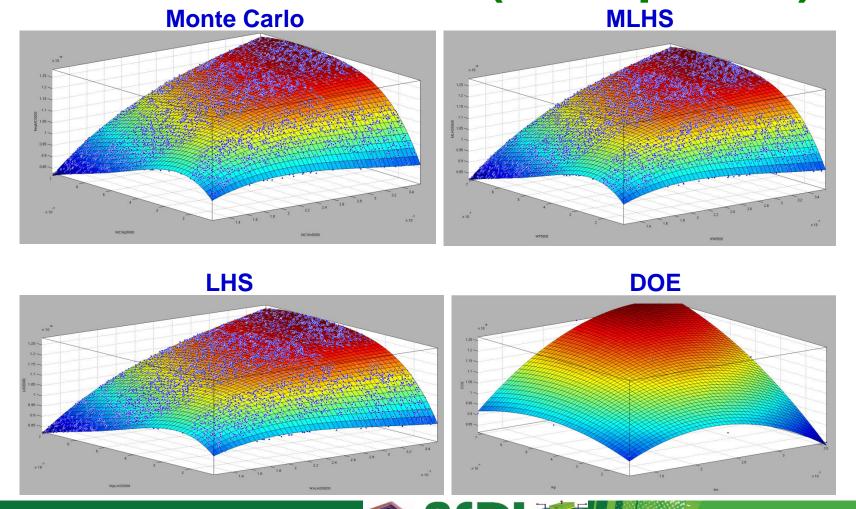

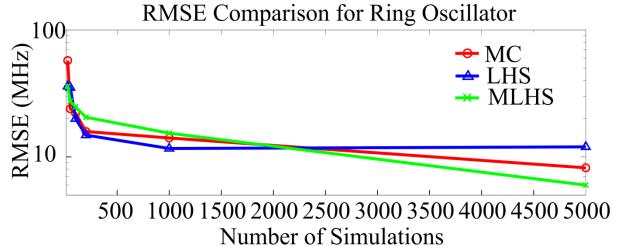

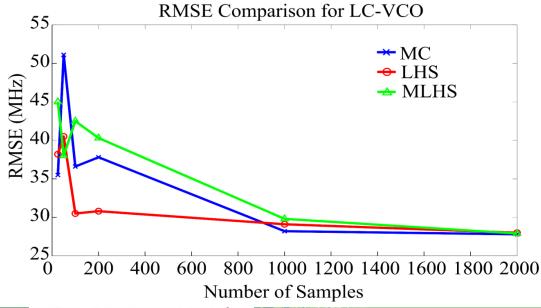

# Sampling Techniques: 45nm Ring Oscillator Circuit (5000 points)

### Sampling Comparison: RO / LC-VCO

#### What do we with iVAMS?

- Use for accurate design verification

- Use for ultra-fast design optimization

### iVAMS-Based Ultrafast Design Flow

A green light to greatness.

# Comparison of the Running Time: 45nm RO Optimization

- Optimization without metamodels: the tabu search optimization is faster by ~1000× than the exhaustive search and ~4× faster than the simulated annealing optimization.

- Optimization with metamodels: the simulated annealing optimization is faster by ~1000× than the exhaustive search and ~6× faster than the tabu search optimization.

#### **Optimization in PLL: Poly Vs NN**

#### **Bee Colony Optimization Results**

| FoM           | Polynomial Metamodel | NN Metamodel |

|---------------|----------------------|--------------|

| Average Power | 3.9 mW               | 3.9 mW       |

| Frequency     | 2.69 GHz             | 2.70 GHz     |

#### **Bee Colony Optimization Time Comparison**

| Algorithm                         | Circuit Netlist                                                          | Polynomial<br>Metamodel           | NN<br>Metamodel                                      |

|-----------------------------------|--------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------|

| Bee Colony<br>(100<br>iterations) | #bees(20) * 5 min * 100 iteration = 10,000 minutes = 7 days (worst case) | 5 mins                            | 0.12 mins                                            |

| Metamodel<br>Generation           | 0                                                                        | 11 hours for LHS + 1 min creation | 11 hours for LHS + 10mins training and verification. |

#### **OP-AMP: Optimization Results**

| Performance      | Constraint | Optimal <sub>POM</sub> | Optimal <sub>SCH</sub> |

|------------------|------------|------------------------|------------------------|

| $A_0$ (dB)       | > 43       | 56.4                   | 52.8                   |

| BW (kHz)         | > 50       | 58.9                   | 85.5                   |

| PM (degree)      | > 70       | 84.4                   | 87.7                   |

| SR (mV/ns)       | > 5        | 7.1                    | 8                      |

|                  | Objective  |                        |                        |

| $P_D$ ( $\mu$ W) | ~ 65       | 65.5                   | 68.1                   |

| Performance          | Optimal <sub>SCH</sub> | Optimal <sub>POM</sub> |

|----------------------|------------------------|------------------------|

| Power Reduction      | ×3.71                  | ×3.86                  |

| Number of iterations | 1200                   | 1200                   |

| Computation Time     | 12.5 h                 | 2.6 s                  |

| Normalized Speed     | 1                      | ×17120                 |

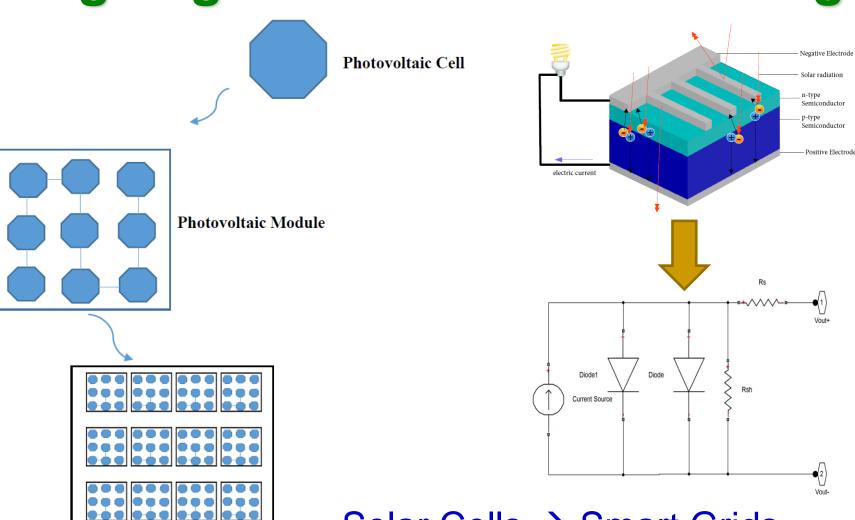

# Ongoing: iVAMS for other "Things"

■ Solar Cells → Smart Grids

A green light to greatness.

**Photovoltaic Array**

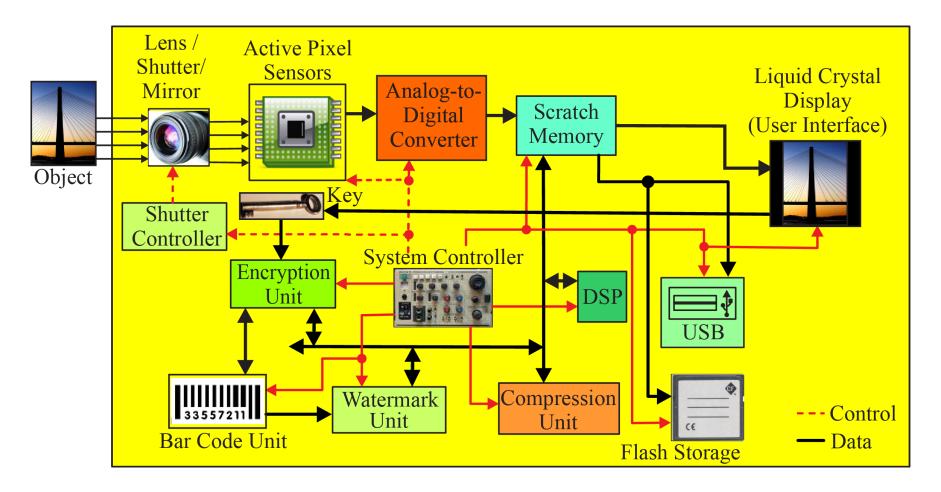

# Ongoing: iVAMS for other "Things"

Secure Digital Camera: For Secure Imaging/Video

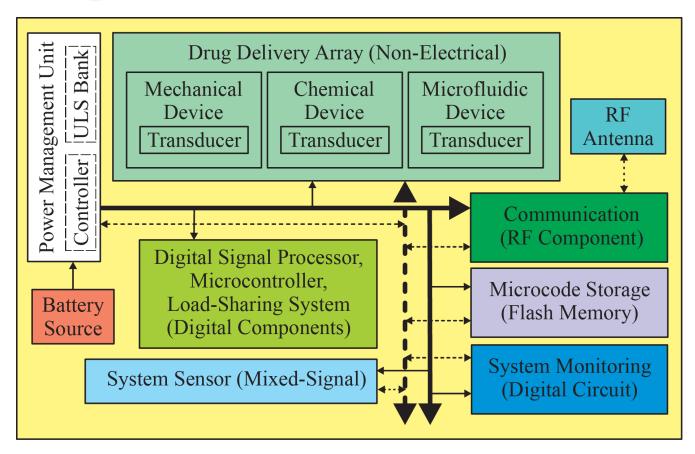

# Ongoing: iVAMS for other "Things"

Nano-Electro-Mechanical-Systems **Smart Health Care**

(NEMS)

#### Conclusions

- IoT components and "Things" have multifold challenges.

- Intelligent Verilog-AMS (iVAMS) is a unique framework for IoT components simulation, verification, and optimization.

- iVAMS can be used for individual components and architecture following hierarchical approach.

- Use of iVAMS and optimization algorithm speed up the design-space exploration for the design.

- Polynomial metamodels are easier create but can be applied for small designs.

- Increase in accuracy is observed using feed forward neural network over polynomial metamodels.

- Kriging and NN metamodels can handle large designs.

- iVAMS for "multidiscipline" "things" needs research.

#### **Some Advertisement**

- Winner of the Association of American Publishers' 2016 PROSE Award in the Textbook in Physical Sciences & Mathematics category.

- Cutting-edge nanoelectronic mixedsignal system design methods

Design discusses mixed-signal circuit and system design based on existing and emerging nanoelectronic technologies. The book features coverage of both digital and analog applications using nanoscale CMOS and post-CMOS. Key techniques required for design for excellence and manufacturability are discussed in this practice-driven text.

**Color lecture slides are available.**

#### References

- S. P. Mohanty, U. Choppali, and E. Kougianos, "Everything You wanted to Know about Smart Cities", *IEEE Consumer Electronics Magazine*, July 2016, pp. .

- S. P. Mohanty, Nanoelectronic Mixed-Signal System Design, McGraw-Hill, 2015, ISBN-10: 0071825711, ISBN-13: 978-0071825719.

- J. A. Stankovic, "Research Directions for the Internet of Things", *IEEE Internet of Things Journal*, Volume: 1, Issue: 1, February 2014.

- O. Okobiah, S. P. Mohanty, and E. Kougianos, "Fast Layout Optimization through Simple Kriging Metamodeling: A Sense Amplifier Case Study", *IEEE Transactions on Very Large Scale Integration* Systems, Volume 22, Issue 4, April 2014, pp. 932--937.

- S. P. Mohanty and E. Kougianos, "Incorporating Manufacturing Process Variation Awareness in Fast Design Optimization of Nanoscale CMOS VCOs", *IEEE Transactions on Semiconductor Manufacturing*, Volume 27, Issue 1, February 2014, pp. 22--31.

- O. Garitselov, S. P. Mohanty, and E. Kougianos, "A Comparative Study of Metamodels for Fast and Accurate Simulation of Nano-CMOS Circuits", *IEEE Transactions on Semiconductor Manufacturing*, Vol. 25, No. 1, Feb 2012, pp. 26--36.

- O. Okobiah, S. P. Mohanty, and E. Kougianos, "Exploring Kriging for Fast and Accurate Design Optimization of Nanoscale Analog Circuits", in *Proceedings of the 13th IEEE Computer Society Annual* Symposium on VLSI, 2014, pp. 244--247.

- G. Zheng, S. P. Mohanty, E. Kougianos, and O. Okobiah, "Polynomial Metamodel Integrated Verilog-AMS for Memristor-Based Mixed-Signal System Design", in *Proceedings of the 56th IEEE International Midwest Symposium on Circuits & Systems*, 2013, pp. 916--919.

- G. Zheng, S. P. Mohanty, E. Kougianos, and O. Okobiah, "iVAMS: Intelligent Metamodel-Integrated Verilog-AMS for Circuit-Accurate System-Level Mixed-Signal Design Exploration", in *Proceedings of the 24th IEEE International Conference on Application-specific Systems, Architectures and Processors*, 2013, pp. 75--78.